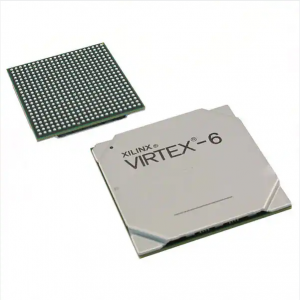

Novu è Originale XC6VLX240T-2FFG1759I Circuit integratu

Attributi di u produttu

| TIPU | DESSCRIPTION |

| categuria | Circuiti integrati (IC) |

| Mfr | AMD Xilinx |

| Serie | Virtex®-6 LXT |

| Pacchettu | vassa |

| Status di u produttu | Attivu |

| Numero di LAB / CLB | 18840 |

| Numeru di elementi logichi / cellule | 241152 |

| Bit di RAM totale | 15335424 |

| Numero di I/O | 720 |

| Tensione - Supply | 0,95 V ~ 1,05 V |

| Tipu di muntatura | Munti superficia |

| Temperature di funziunamentu | -40 °C ~ 100 °C (TJ) |

| Pacchettu / Casu | 1759-BBGA, FCBGA |

| Paquet di Dispositivi Fornitore | 1759-FCBGA (42,5 × 42,5) |

| U numeru di produttu di basa | XC6VLX240 |

Documenti & Media

| TIPU DI RESOURCE | LINK |

| Datasheets | Scheda dati Virtex-6 FPGA |

| Moduli di furmazione di produttu | Virtex-6 FPGA Panoramica |

| L'infurmazione ambientale | Xiliinx RoHS Cert |

| Disegnu / Specifica PCN | Avvisu senza piombo di navi incruciate 31/Oct/2016 |

Classificazioni Ambientali è Export

| ATTRIBUTU | DESSCRIPTION |

| Status RoHS | Conforme à ROHS3 |

| Livellu di sensibilità à l'umidità (MSL) | 4 (72 ore) |

| Status REACH | REACH ùn hè micca affettatu |

| ECCN | 3A001A7A |

| HTSUS | 8542.39.0001 |

XC6VLX240T-2FFG1759I Panoramica di FPGA

L'FPGA XC6VLX240T-2FFG1759I sò a fundazione di silicuu programabile per e Piattaforme di Design Targeted chì furniscenu cumpunenti di software è hardware integrati per permette à i disegnatori di fucalizza nantu à l'innuvazione appena principia u so ciclu di sviluppu.Utilizendu l'architettura basata in colonna ASMBL (Advanced Silicon Modular Block) di terza generazione, u Xilinx XC6VLX240T-2FFG1759I cuntene assai blocchi integrati à livellu di sistema.Queste caratteristiche permettenu à i diseggiani logichi di custruisce i più alti livelli di prestazione è funziunalità in i so sistemi basati in FPGA.Custruiti nantu à una tecnulugia di prucessu di rame di punta di 40 nm, XC6VLX240T-2FFG1759I FPGA sò una alternativa programabile à a tecnulugia ASIC persunalizata.offre a megliu soluzione per affruntà i bisogni di i disegnatori di logica d'altu rendimentu, di i disegnatori di DSP d'altu rendiment è di i disegnatori di sistemi integrati d'altu rendimentu cù una logica senza precedente, DSP, connettività è capacità di microprocessore soft.

A serie Xilinx FPGAs (Field Programmable Gate Array) XC6VLX240T-2FFG1759I hè Virtex-6 LXT FPGA 720 I/O 1759FCBGA, Vede i Sostituti è Alternative inseme cù datasheets, stock, prezzi da Distributori Autorizzati in FPGAkey.com. altri prudutti FPGAs.

Features

Trè sottofamiglie:

FPGA Virtex-6 LXT: logica d'alta prestazione cù connettività seriale avanzata

FPGA Virtex-6 SXT: A più alta capacità di trasfurmazione di u signale cù una connettività seriale avanzata

FPGA Virtex-6 HXT: Connettività seriale di larghezza di banda più alta

Compatibilità trà sub-famiglie

I dispositi LXT è SXT sò impronte cumpatibili in u stessu pacchettu

Logica FPGA avanzata, ad alte prestazioni

Tecnulugia vera di a tabella di ricerca di 6 input (LUT).

Opzione doppia LUT5 (LUT a 5 ingressi).

Coppia LUT/dual flip-flop per applicazioni chì necessitanu un mix di registru riccu

Efficienza di routing mejorata

Opzione di RAM LUT distribuita a 64 bit (o due a 32 bit) per LUT a 6 ingressi

SRL32/dual SRL16 cù l'opzione di outputs registrati

Putenti gestori di clock in modalità mista (MMCM)

I blocchi MMCM furniscenu buffering di ritardu zero, sintesi di frequenza, shifting di fase di clock, filtrazione di inputjitter, è divisione di clock matched phase.

36-Kb bloccu RAM / FIFOs

Tecnulugia SelectIO parallela di altu rendiment

Slice avanzate DSP48E1

Opzioni di cunfigurazione flessibili

Interfaccia SPI è Parallel Flash

Supportu multi-bitstream cù logica di ricunfigurazione di fallback dedicata

Rilevazione automatica di larghezza di bus

Capacità di Monitor di Sistema in tutti i dispositi

Surveillance termica è di tensione di furnimentu in chip / off-chip

Accessu JTAG à tutte e quantità monitorate

Blocchi d'interfaccia integrati per i disinni PCI Express

Transceivers GTX: finu à 6,6 Gb/s

Tassi di dati sottu à 480 Mb/s supportati da u oversampling in a logica FPGA.

Transceivers GTH: 2,488 Gb/s à oltre 11 Gb/s

Bloccu MAC Ethernet 10/100/1000 Mb/s integratu

Supporta 1000BASE-X PCS/PMA è SGMII cù transceivers GTX

Supporta MII, GMII è RGMII utilizendu risorse di tecnulugia SelectIO

Supportu 2500 Mb/s dispunibule

Tecnulugia di prucessu CMOS di cobre 40 nm

Tensione core 1.0V (solu gradi di velocità -1, -2, -3)

Opzione di tensione di core di bassa putenza 0.9V (solu di gradu di velocità -1L)

Imballaggio flip-chip d'alta integrità di signale dispunibule in opzioni di pacchettu standard o senza Pb