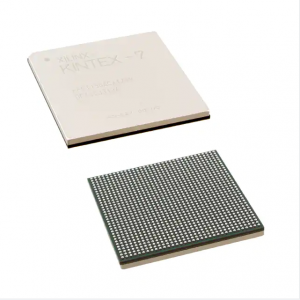

Xilinx/XC7K480T-2FFG1156I/XC7K480T/IC BOM FPGA/circuitu integratu

Specificazioni

| Attributu di u produttu | Valore di l'attributu |

| Produttore: | Xilinx |

| Categoria di produttu: | FPGA - Array di porta programmabile in u campu |

| RoHS: | Dettagli |

| Serie: | XC7K480T |

| Numero di elementi logici: | 477760 LE |

| Numero di I/O: | 400 I/O |

| Tensione di alimentazione - Min: | 1 V |

| Tensione di alimentazione - Max: | 1 V |

| Température minimale de fonctionnement : | - 40 C |

| Temperature Maximum Operating: | + 100 C |

| Tariffa di dati: | 12,5 Gb/s |

| Numero di trasmettitori: | 32 Transceiver |

| Stile di muntatura: | SMD/SMT |

| Pacchettu / Casu: | FCBGA-1156 |

| Marca: | Xilinx |

| RAM distribuita: | 6788 kbit |

| RAM di blocchi integrati - EBR: | 34380 kbit |

| Frequenza operativa massima: | 640 MHz |

| Sensibili à l'umidità: | Iè |

| Numero di blocchi di array logicu - LAB: | 37325 LAB |

| Tensione di alimentazione operativa: | 1 V |

| Tipu di pruduttu: | FPGA - Array di porta programmabile in u campu |

| Quantità di pacchettu di fabbrica: | 1 |

| Subcategoria: | IC logici programmabili |

| Nome commerciale: | Kintex |

Panoramica di l'FPGA XC7K480T-2FFG1156I

Descrizzione generale

I FPGA di a serie Xilinx® 7 comprendenu quattru famiglie FPGA chì indirizzanu a gamma completa di esigenze di u sistema, chì varieghja da u prezzu bassu, fattore di forma chjuca, applicazioni sensibili à u costu, di voluminu elevatu à larghezza di banda di connettività ultra high-end, capacità logica è capacità di trasfurmazioni di signali. per l'applicazioni d'alta prestazione più esigenti.I FPGA di a serie 7 includenu:

• Famiglia Spartan®-7: Optimized per low cost, putenza più bassu, è altu rendiment I / O.Disponibile in un imballaggio low-cost, assai picculu fattore di forma per u più chjucu impronta di PCB.

• Famiglia Artix®-7: Ottimizata per l'applicazioni di bassa putenza chì necessitanu transceivers seriali è altu DSP è throughput logicu.Fornisce u più bassu costu tutale di materiali per l'applicazioni d'alta produzzione è sensibili à i costi.

• Famiglia Kintex®-7: Optimized per u megliu prezzu-prestazioni cù una migliione 2X cumparatu à a generazione precedente, chì permette una nova classa di FPGA.

• Famiglia Virtex®-7: Optimized per u più altu rendiment di u sistema è a capacità cù una mellura 2X in u rendiment di u sistema.Dispositivi di più alta capacità attivati da a tecnulugia di interconnessione di siliciu impilatu (SSI).

Custruitu annantu à una tecnulugia di prucessu di avanzata, alta prestazione, bassa putenza (HPL), 28 nm, high-k metal gate (HKMG), FPGA di serie 7 permettenu un aumentu senza pari in u rendiment di u sistema cù 2.9 Tb/ s di larghezza di banda I / O, 2 milioni di capacità di cellula logica, è 5.3 TMAC / s DSP, mentre cunsumendu 50% menu energia di i dispositi di generazione precedente per offre una alternativa cumplettamente programabile à ASSP è ASIC.

Features

• Lògica FPGA d'alta prestazione avanzata basata nantu à a vera tecnulugia di tavola di ricerca di 6 input (LUT) configurabile cum'è memoria distribuita.

• 36 Kb dual-port block RAM with built-in FIFO logic for on-chip data buffering.

• Tecnulugia SelectIO™ d'altu rendiment cù supportu per interfacce DDR3 finu à 1,866 Mb/s.

• Connettività seriale d'alta velocità cù transceivers multi-gigabit integrati da 600 Mb/s à tassi massimi di 6,6 Gb/s à 28,05 Gb/s, chì offre un modu speciale di bassa putenza, ottimizzatu per interfacce chip-to-chip .

• Una interfaccia analogica configurabile d'utilizatore (XADC), chì incorpora cunvertitori analogici-digitali duali 12-bit 1MSPS cù sensori termichi è di furnizzioni in chip.

• DSP fette cù multiplicatori 25 x 18, accumulatore 48-bit, è pre-adder per filtrazione d'altu rendiment, cumpresu filtrazione di coefficienti simmetrici ottimizzati.

• Tiles di gestione di clock potenti (CMT), cumminendu un loop in fase di bloccu (PLL) è blocchi di gestione di clock in modalità mixta (MMCM) per alta precisione è jitter bassu.

• Bloccu integratu per PCI Express® (PCIe), finu à x8 Gen3 Endpoint and Root Port designs.

• Una larga varietà di opzioni di cunfigurazione, cumprese supportu per i ricordi di merceria, criptografia AES 256-bit cù autentificazione HMAC/SHA-256, è rilevazione è correzione SEU integrata.

• Low-cost, wire-bond, lidless flip-chip, è imballaggio flipchip di alta integrità di signale chì offre una migrazione faciule trà i membri di a famiglia in u stessu pacchettu.Tutti i pacchetti dispunibili in Pb-free è pacchetti selezziunati in l'opzione Pb.

• Cuncepitu per un altu rendiment è u putere più bassu cù 28 nm, HKMG, prucessu HPL, tecnulugia di prucessu di tensione di core 1.0V è opzione di tensione di core 0.9V per un putere ancu più bassu.

A serie XC7K480T-2FFG1156I di Xilinx FPGAs (Field Programmable Gate Array) hè FPGA, Kintex-7, MMCM, PLL, 400 I/O, 710 MHz, 477760 Cells, 970 mV à 1.03 V è Sostituti 1.03 V, FCBGA-11, Alternative, FCBGA-11 cù datasheets, stock, pricing da i Distributori Autorizzati in FPGAkey.com, è pudete ancu circà altri prudutti FPGAs.

Features

Logica FPGA avanzata d'alta prestazione basata nantu à a vera tecnulugia di tavola di ricerca di 6 input (LUT) configurabile cum'è memoria distribuita.

36 Kb RAM di bloccu duale portu cù logica FIFO integrata per buffering di dati in chip.

Tecnulugia SelectIO d'alta prestazione cù supportu per interfacce DDR3 finu à 1,866 Mb/s.

Connettività seriale à alta velocità cù transceivers multi-gigabit integrati da 600 Mb/s à tassi massimi di 6,6 Gb/s à 28,05 Gb/s, chì offre un modu speciale di bassa putenza, ottimizzatu per interfacce chip-to-chip.

Una interfaccia analogica configurabile da l'utilizatore (XADC), chì incorpora un convertitore analogico-digitale duale 12-bit 1MSPS cù sensori termichi è di fornitura in chip.

Slices DSP cun multiplicatore 25 x 18, accumulatore di 48 bit, è pre-adder per un filtramentu d'altu rendiment, cumpresu un filtramentu di coefficient simmetricu ottimizzatu.

Piastrelle di gestione di clock potenti (CMT), cumminendu un loop in fase bloccata (PLL) è blocchi di gestione di clock in modalità mixta (MMCM) per alta precisione è jitter bassu.

Bloccu integratu per PCI Express (PCIe), finu à x8 Gen3 Endpoint è disinni Root Port.

Ampia varietà di opzioni di cunfigurazione, cumprese supportu per i ricordi di merceria, criptografia AES a 256-bit cù autentificazione HMAC/SHA-256, è rilevazione è correzione SEU integrata.

Imballaggio flipchip à pocu costu, filu-bond, senza coperchio, è imballaggio flipchip d'alta integrità di signale chì offre una migrazione faciule trà i membri di a famiglia in u stessu pacchettu.Tutti i pacchetti dispunibuli in Pb-free è pacchetti selezziunati in l'opzione Pb.

Cuncepitu per altu rendiment è putenza più bassu cù 28 nm, HKMG, prucessu HPL, tecnulugia di prucessu di tensione di core 1.0V è opzione di tensione di core 0.9V per una putenza ancu più bassa.