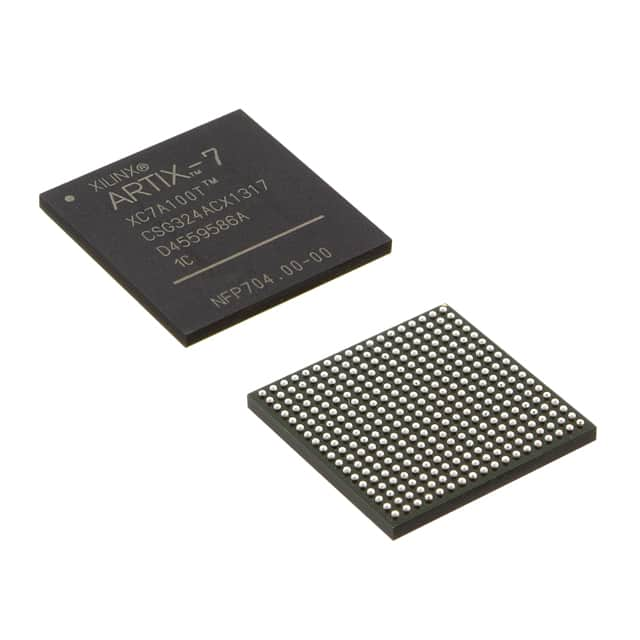

Chip IC originale programmabile XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

Attributi di u produttu

| TIPU | DESSCRIPTION |

| categuria | Circuiti integrati (IC) |

| Mfr | AMD Xilinx |

| Serie | Virtex® UltraScale™ |

|

| Scatola |

| Standardd Pacchettu | 1 |

| Status di u produttu | Attivu |

| Numero di LAB / CLB | 316620 |

| Numeru di elementi logichi / cellule | 5540850 |

| Bit di RAM totale | 90726400 |

| Numero di I/O | 1456 |

| Tensione - Supply | 0.922V ~ 0.979V |

| Tipu di muntatura | Munti superficia |

| Temperature di funziunamentu | -40 °C ~ 100 °C (TJ) |

| Pacchettu / Casu | 2892-BBGA, FCBGA |

| Paquet di Dispositivi Fornitore | 2892-FCBGA (55×55) |

| U numeru di produttu di basa | XCVU440 |

Utilizà FPGA cum'è processori di trafficu per a sicurità di a rete

U trafficu da è da i dispositi di sicurità (firewalls) hè criptatu à parechji livelli, è a criptografia / decifrazione L2 (MACSec) hè trattata à i nodi di rete di u ligame (L2) (switch è router).L'elaborazione oltre l'L2 (layer MAC) include tipicamente un'analisi più profonda, a decifrazione di tunnel L3 (IPSec) è u trafficu SSL cifratu cù u trafficu TCP / UDP.L'elaborazione di pacchetti implica l'analisi è a classificazione di i pacchetti entranti è l'elaborazione di grandi volumi di trafficu (1-20M) cù un altu throughput (25-400Gb/s).

A causa di u gran numaru di risorse di computing (core) necessarii, NPU ponu esse aduprati per un processamentu di pacchetti di velocità relativamente più altu, ma a bassa latenza, u processu di trafficu scalabile d'altu rendimentu ùn hè micca pussibule perchè u trafficu hè processatu cù core MIPS / RISC è scheduling such cores. basatu nantu à a so dispunibilità hè difficiule.L'usu di l'apparecchi di sicurezza basati in FPGA pò eliminà in modu efficace queste limitazioni di l'architetture basate in CPU è NPU.

Trattamentu di sicurezza à livellu di l'applicazione in FPGA

I FPGA sò ideali per l'elaborazione di sicurezza in linea in firewall di prossima generazione perchè rispondenu cù successu à a necessità di un rendimentu più altu, flessibilità è operazione di bassa latenza.Inoltre, i FPGA ponu ancu implementà funzioni di sicurezza à livellu di l'applicazione, chì ponu ancu risparmià risorse di l'informatica è migliurà u rendiment.

Esempi cumuni di trasfurmazioni di sicurezza di l'applicazioni in FPGA includenu

- Mutore di scaricamentu TTCP

- Corrispondenza di l'espressione regulare

- Trattamentu di criptografia asimmetrica (PKI).

- Trattamentu TLS

Tecnulugie di sicurezza di a prossima generazione chì utilizanu FPGA

Numerosi algoritmi asimmetrici esistenti sò vulnerabili à u cumprumissu da i computer quantistici.L'algoritmi di sicurezza asimmetrici cum'è RSA-2K, RSA-4K, ECC-256, DH è ECCDH sò i più affettati da e tecniche di computazione quantistica.Nove implementazioni di algoritmi asimmetrici è standardizazione NIST sò state esplorate.

I pruposti attuali per a criptografia post-quantum includenu u metudu Ring-on-Error Learning (R-LWE) per

- Criptografia di chjave publica (PKC)

- Firme digitale

- Creazione di chjave

L'implementazione pruposta di a criptografia di chjave publica include certe operazioni matematiche ben cunnisciute (TRNG, sampler di rumore gaussianu, addizione polinomiale, divisione di quantificatore polinomiale binariu, multiplicazione, etc.).L'IP FPGA per parechji di questi algoritmi hè dispunibule o pò esse implementatu in modu efficiente utilizendu blocchi di costruzione FPGA, cum'è i motori DSP è AI (AIE) in i dispositi Xilinx esistenti è di prossima generazione.

Stu libru biancu descrive l'implementazione di a sicurità L2-L7 utilizendu una architettura programabile chì pò esse implementata per l'accelerazione di sicurezza in e rete di bordu / accessu è firewall di prossima generazione (NGFW) in rete d'impresa.