5CEFA7F31I7N chips ic novi è originali circuiti integrati cumpunenti elettronici u megliu prezzu unu spot cumprà serviziu BOM

Attributi di u produttu

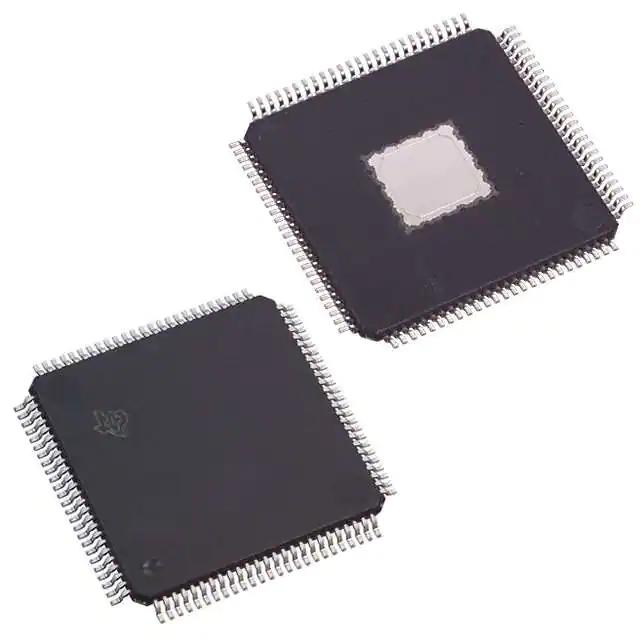

| TIPU | DESSCRIPTION |

| categuria | Circuiti integrati (IC) |

| Mfr | Intel |

| Serie | Cyclone® VE |

| Pacchettu | vassa |

| Paquet Standard | 27 |

| Status di u produttu | Attivu |

| Numero di LAB / CLB | 56480 |

| Numeru di elementi logichi / cellule | 149500 |

| Bit di RAM totale | 7880704 |

| Numero di I/O | 480 |

| Tensione - Supply | 1.07V ~ 1.13V |

| Tipu di muntatura | Munti superficia |

| Temperature di funziunamentu | -40 °C ~ 100 °C (TJ) |

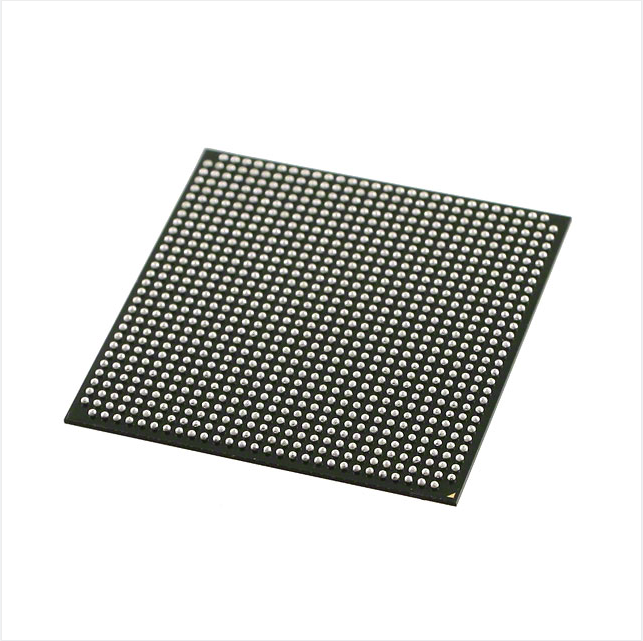

| Pacchettu / Casu | 896-BGA |

| Paquet di Dispositivi Fornitore | 896-FBGA (31×31) |

| U numeru di produttu di basa | 5CEFA7 |

1. FPGA di a serie Virtex per un altu rendiment

A serie Virtex hè u pruduttu high-end di Xilinx è u primu pruduttu in l'industria.Xilinx hà vintu u mercatu cù i so prudutti di a serie Virtex, ottenendu cusì a pusizione cum'è u primu fornitore FPGA.Si pò dì chì Xilinx guida l'industria di l'array di porta programmabile in u campu cù a so famiglia Virtex di prudutti FPGA.Hè principalmente destinatu à l'applicazioni cum'è l'infrastruttura di telecomunicazione, l'industria automobilistica è l'elettronica di cunsumu high-end.L'attuale chip mainstream include Vitrex-2, Virtex-2 Pro, Virtex-4, Virtex-5, Virtex-6, è Virtex-7 categurie.

A serie Virtex-2 hè statu introduttu in u 2002 cù un prucessu di 0.15nm, tensione di core 1.5V, clock operativi finu à 420MHz, supportu per più di 20 standard di interfaccia I/O, capacità di gestione di clock di u sistema cumpletu, è core IP integratu. Tecnulugia di core chì permette à i nuclei IP duri per esse assignati in ogni locu nantu à u chip, cù più risorse è prestazioni più altu ch'è a serie Virtex.prestazioni più altu ch'è a famiglia Virtex.

A serie Virtex-2 Pro si basa nantu à u Virtex-2 cù capacità di trasfurmazioni integrate avanzate, è core PowerPC405 integrati, è include tecnulugia avanzata di interconnessione attiva per affruntà e sfide affrontate da i sistemi d'alta prestazione, in più di l'aghjunzione di una alta velocità. transceiver seriale per furnisce soluzioni Gigabit Ethernet.

A famiglia Virtex-4 hè basatu annantu à l'architettura Advanced Silicon Block Combination Module (ASMBL), chì presenta una alta densità logica cù frequenze di clock finu à 500 MHz;cù moduli DCM, divisori di clock di corrispondenza di fasi PMCD, rete di clock differenziali in chip;Tecnulugia SmartRAM 500 MHz cù logica di cuntrollu FIFO integrata, è ogni I / O hè integratu cù a tecnulugia di sincronizazione di fonte ChipSync per 1 Gbps I / O è chip logicu Xtreme DSP.I disegnatori ponu selezziunà diversi sottosistemi Virtex-4 secondu i so bisogni, per disinni intensivi di logica: Virtex-4 LX, per applicazioni di trasfurmazioni di signali d'alta prestazione: Virtex-4 SX, per connettività seriale d'alta velocità è applicazioni di trasfurmazioni integrate: Virtex- 4 FX.A famiglia Virtex-4 offre una mellura significativa in tutte e metriche nantu à VirtexII A serie Virtex-4, chì hè stata in produzzione di massa da a fine di u 2005, hà rimpiazzatu u VirtexII, VirtexII-Pro, è hè u pruduttu più impurtante di Xilinx in l'altitudine di l'oghje. -fini u mercatu FPGA.

A famiglia Virtex-5 hè basatu annantu à a tecnulugia di prucessu di rame 65nm di punta è usa una architettura colonnare ASMBL (Advanced Silicon Building Block) di seconda generazione, chì cuntene cinque piattaforme distinte (sottofamiglie).Ogni piattaforma cuntene diverse proporzioni di funzioni per risponde à i bisogni di parechji disinni logici avanzati.In più di l'architettura logica d'alta prestazione di punta, i FPGA Virtex-5 includenu una varietà di moduli à livellu di sistema hard-IP, cumprese un putente 36 Kb Block RAM / FIFO, una seconda generazione 25 × 18. DSP Slice, tecnulugia SelectIO cù impedenza CNC integrata, moduli di interfaccia di sincronizazione di fonti ChipSync, funziunalità di monitor di u sistema, è generatori di clock integrati DCM (Digital Clock Manager) è PLL (Phase Locked Loop), è opzioni di cunfigurazione avanzate.Altre caratteristiche basate nantu à a piattaforma includenu un modulu transceiver seriale d'alta velocità ottimizzatu per a putenza per una connettività seriale rinfurzata, un modulu endpoint integratu compatibile cù PCI Express, un MAC Ethernet tri-state (controller d'accessu à i media), è un microprocessore PowerPC 440 d'altu rendiment. modulu integratu chì permette à i diseggiani logici avanzati di incarnà i più alti livelli di prestazione in i so sistemi basati in FPGA.

A famiglia Virtex-6 offre l'ultime funzioni più avanzate à u mercatu FPGA.I FPGA Virtex-6 sò a fundazione di a tecnulugia di siliciu programabile per i testbeds di destinazione chì furniscenu cumpunenti hardware è software per aiutà i disegnatori à fucalizza nantu à l'innuvazione una volta chì i sforzi di sviluppu sò stati iniziati.A famiglia Virtex-6 presenta una architettura di pilastri ASMBL di terza generazione (modulu di portfolio di siliciu avanzatu) chì include parechje sottofamiglie diverse.Questa panoramica descrive i dispositi in i subfamiglie LXT, SXT è HXT.Ogni sottofamiglia cuntene una diversa cumminazione di funzioni per risponde in modu efficiente à una larga gamma di esigenze di cuncepimentu logicu avanzatu.In più di u tessulu logicu d'altu rendiment, i FPGA Virtex-6 includenu parechji moduli integrati à livellu di sistema.Queste caratteristiche permettenu à i diseggiani logici di custruisce i più alti livelli di prestazione è funziunalità in i so sistemi FPGA.I FPGA Virtex-6 furniscenu ancu a megliu soluzione per risponde à i bisogni di i disegnatori di logica d'altu rendimentu, di i disegnatori di DSP d'altu rendiment è di i disegnatori di sistemi integrati d'altu rendiment, purtendu una logica senza precedente, DSP, connettività è capacità di microprocessore soft.

Virtex-7 hè un pruduttu FPGA ultra-high-end introduttu in 2011 nantu à un prucessu 28nm chì dà à i clienti a libertà di tuck and untangle features that reduce cost and power consume while increase performance and capacity, riducendu cusì l'investimenti di sviluppu è di implementazione per i dui bassi. -costu è famiglie di altu rendiment.Inoltre, una riduzione di u costu di 35% in paragunà à Virtex-6 hè assicurata senza cunversione incrementale o investimentu in ingegneria, aumentendu ancu a produtividade.

.png)