SN74ACT244PWR 8-ch, 4.5-V à 5.5-V buffers cù ingressi CMOS TTL-compatibili è uscite à 3 stati

Attributi di u produttu

| UE RoHS | Conforme |

| ECCN (US) | EAR99 |

| Status di parte | Attivu |

| HTS | 8542.39.00.01 |

| Automotive | No |

| PPAP | No |

| Famiglia logica | ACT |

| Funzione logica | Buffer/Line Driver |

| Numero di elementi per chip | 2 |

| Numero di canali per chip | 8 |

| U numeru di inputs per chip | 8 |

| Numeru di abilitazioni di input per chip | 0 |

| Numero di outputs per chip | 8 |

| Numero di attivazioni di output per chip | 2 Bassu |

| Bus Hold | No |

| Polarità | Non-inversione |

| Tempu di Ritardo Massimu di Propagazione @ CL Massimu (ns) | 9@4.5V to 5.5V |

| Tempu di Ritardo di Propagazione Assoluta (ns) | 10.5 |

| Tecnulugia di prucessu | CMOS |

| Tipu di signale di input | Single-Ended |

| Tipu di output | 3-Statu |

| Corrente Massima di Salita di Livellu Bassu (mA) | 24 |

| Corrente di Output Massima Altu Livellu (mA) | -24 |

| Tensione d'alimentazione minima di u funziunamentu (V) | 4.5 |

| Tensione di alimentazione tipica (V) | 5 |

| Tensione massima di alimentazione operativa (V) | 5.5 |

| I/O tolleranti (V) | 5.5 Ingressi |

| Corrente di riposu massimu (uA) | 4 |

| Cundizione di prova di ritardu di propagazione (pF) | 50 |

| Température minimale de fonctionnement (°C) | -40 |

| Température maximale de fonctionnement (°C) | 85 |

| Grade di temperatura di u fornitore | Cummerciale |

| Imballaggio | Tape è Reel |

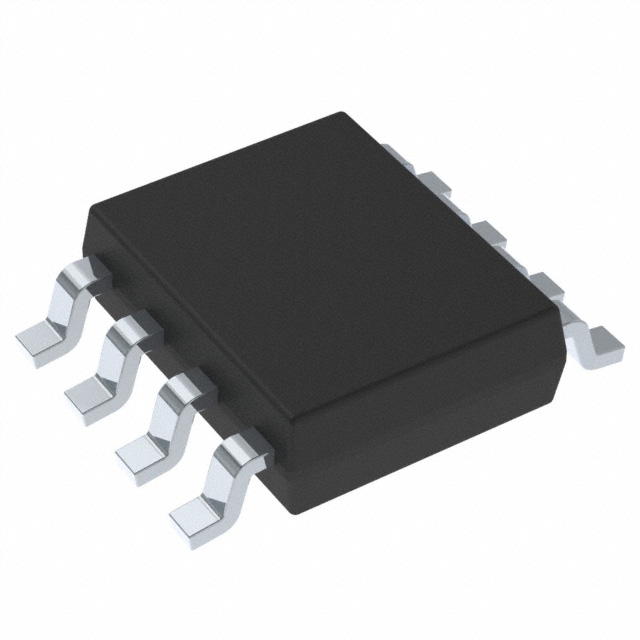

| Muntà | Munti superficia |

| Altezza di u pacchettu | 1,05 (max) |

| Larghezza di u pacchettu | 4,5 (max) |

| Lunghezza di u pacchettu | 6,6 (max) |

| PCB cambiatu | 20 |

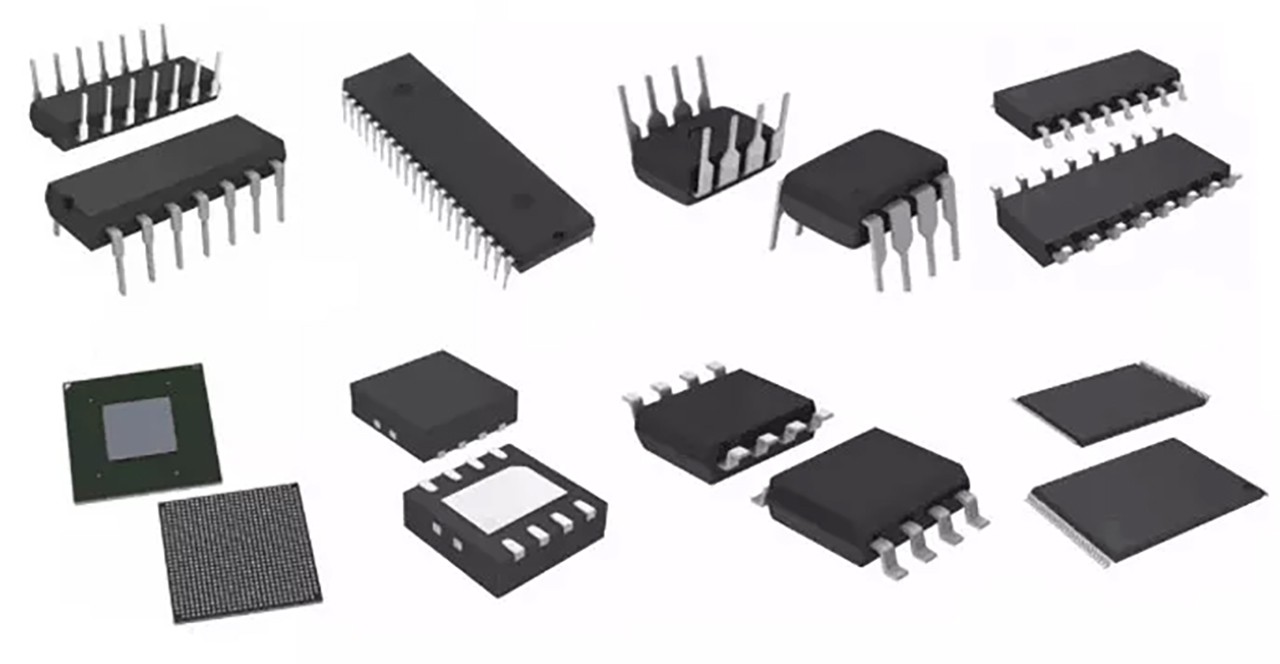

| Nome di u pacchettu standard | SOP |

| Pacchettu Supplier | TSSOP |

| Pin Count | 20 |

| Forma di piombo | Ala di gabbiana |

Introduzione dettagliata

Questi buffer ottali SNx4ACT244 è drivers sò cuncepiti specificamente per migliurà u rendiment è a densità di i driver d'indirizzu di memoria di 3 stati, i driver di clock, è i ricevitori è trasmettitori orientati à l'autobus.I dispositi SNx4ACT244 sò urganizati cum'è dui buffer di 4 bit è drivers cù inputs di output-enable (OE) separati.Quandu l'OE hè bassu, u dispusitivu passa dati micca invertiti da l'inputs A à l'outputs Y.Quandu OE hè altu, i outputs sò in u statu di alta impedenza.

Scrivite u vostru missaghju quì è mandate à noi